有別於過往的「大小核」稱呼,Intel 於 Architecture Day 2021(2021 架構日)正式定名 Alder Lake 處理器中的兩種核心,分別是 Performance Core (P-Core) 效能核心 與 Efficient Core (E-Core) 效率核心。

Efficient Core (E-Core) 效率核心

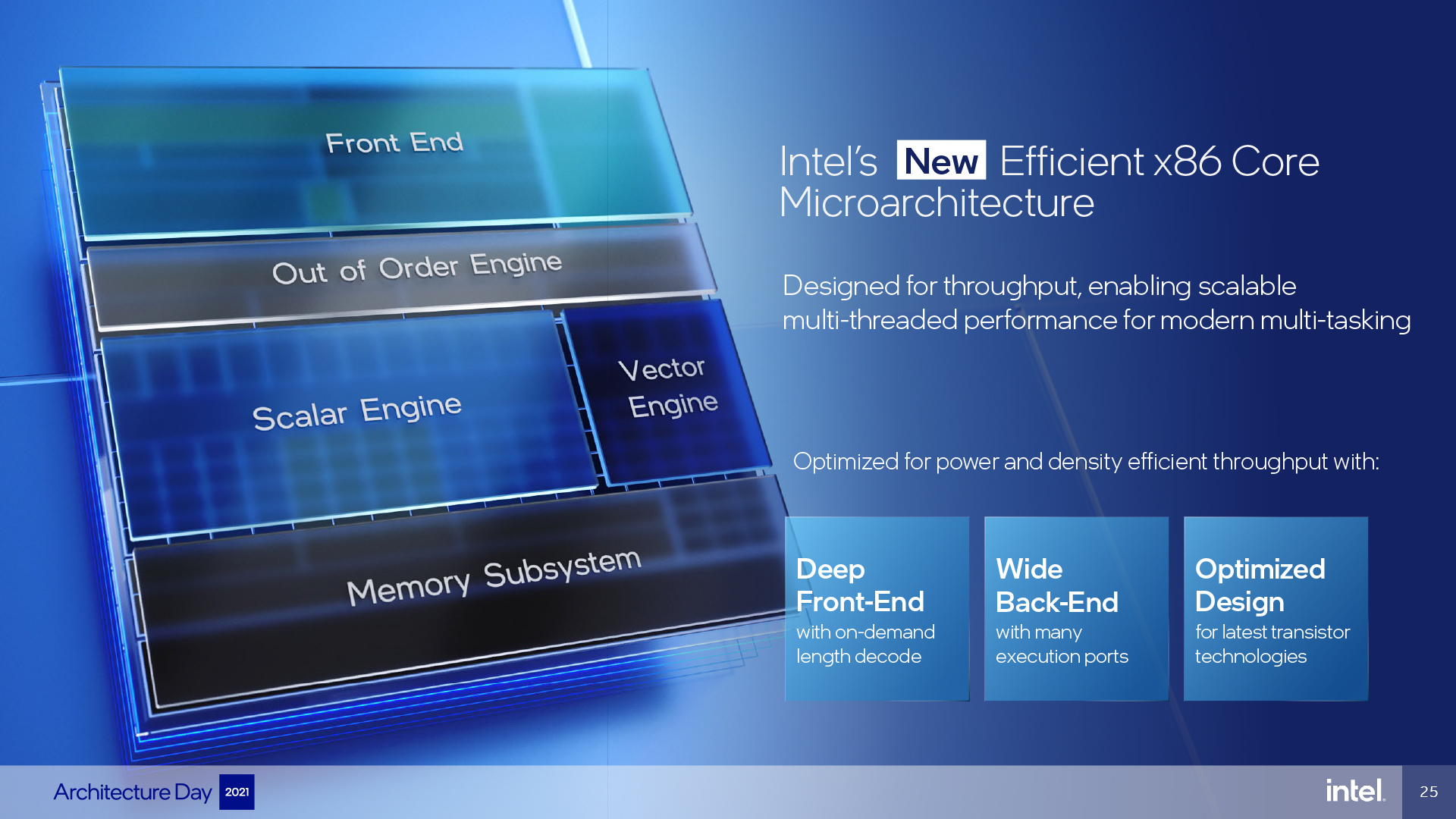

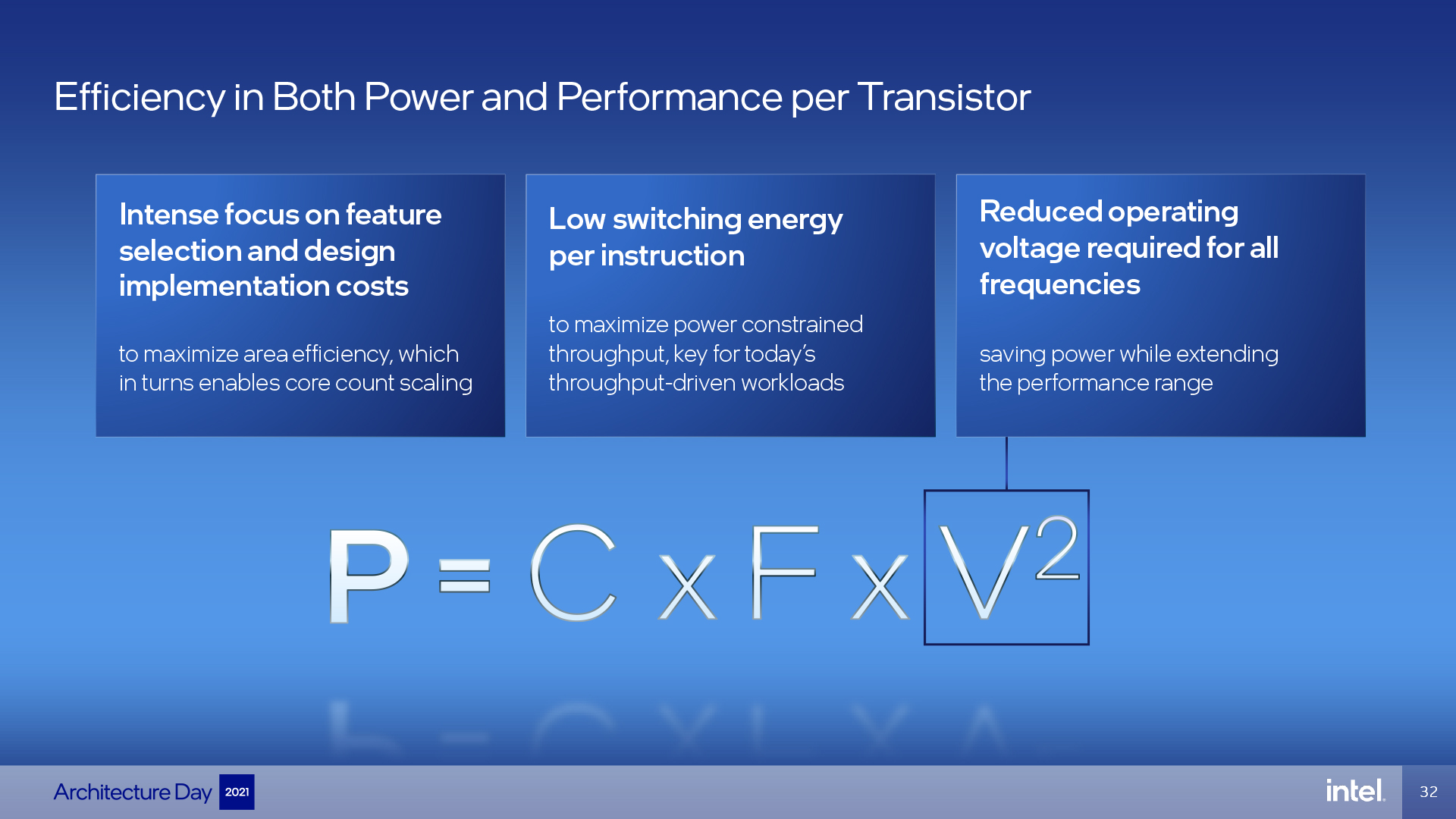

效率核心微架構先前的代號為 Gracemont,專為吞吐量效率而設計,儘可能極小化晶圓面積但依舊可讓多執行緒效能可隨著核心數量成長。它提供廣泛的運作時脈範圍,也允許核心在低電壓環境中運作降低功耗。

主要特性有:

- 5000 條分支目標快取,達成更為精確的分支預測。

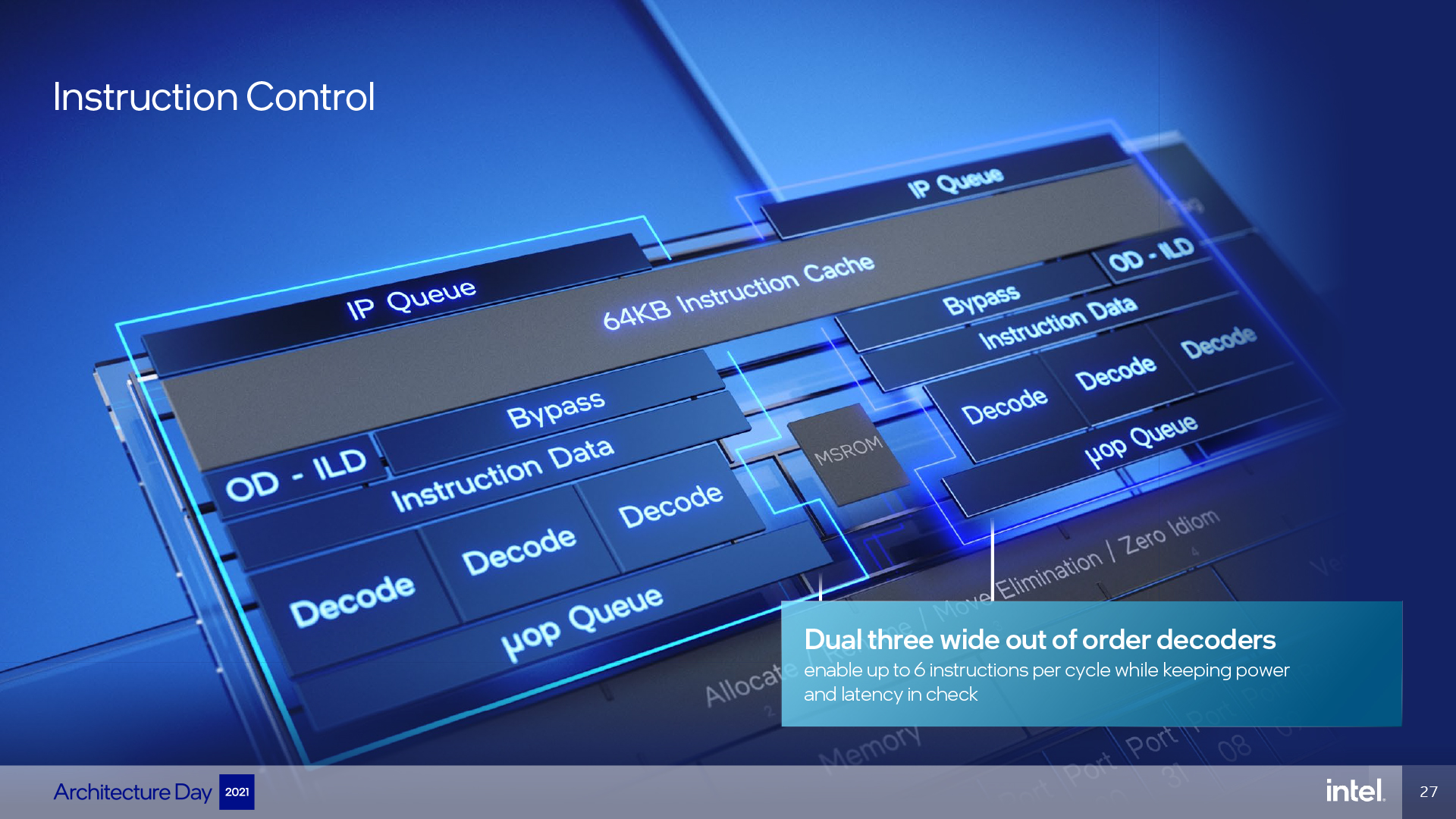

- 64 KB 指令快取,將有用的指令放在距離較近之處,避免額外產生記憶體子系統的功耗。

- 首度導入隨選型指令長度解碼器,負責產生預解碼資訊。

- 叢集亂序解碼器於維持電力效率的同時,每週期最高能夠解碼 6 條指令。

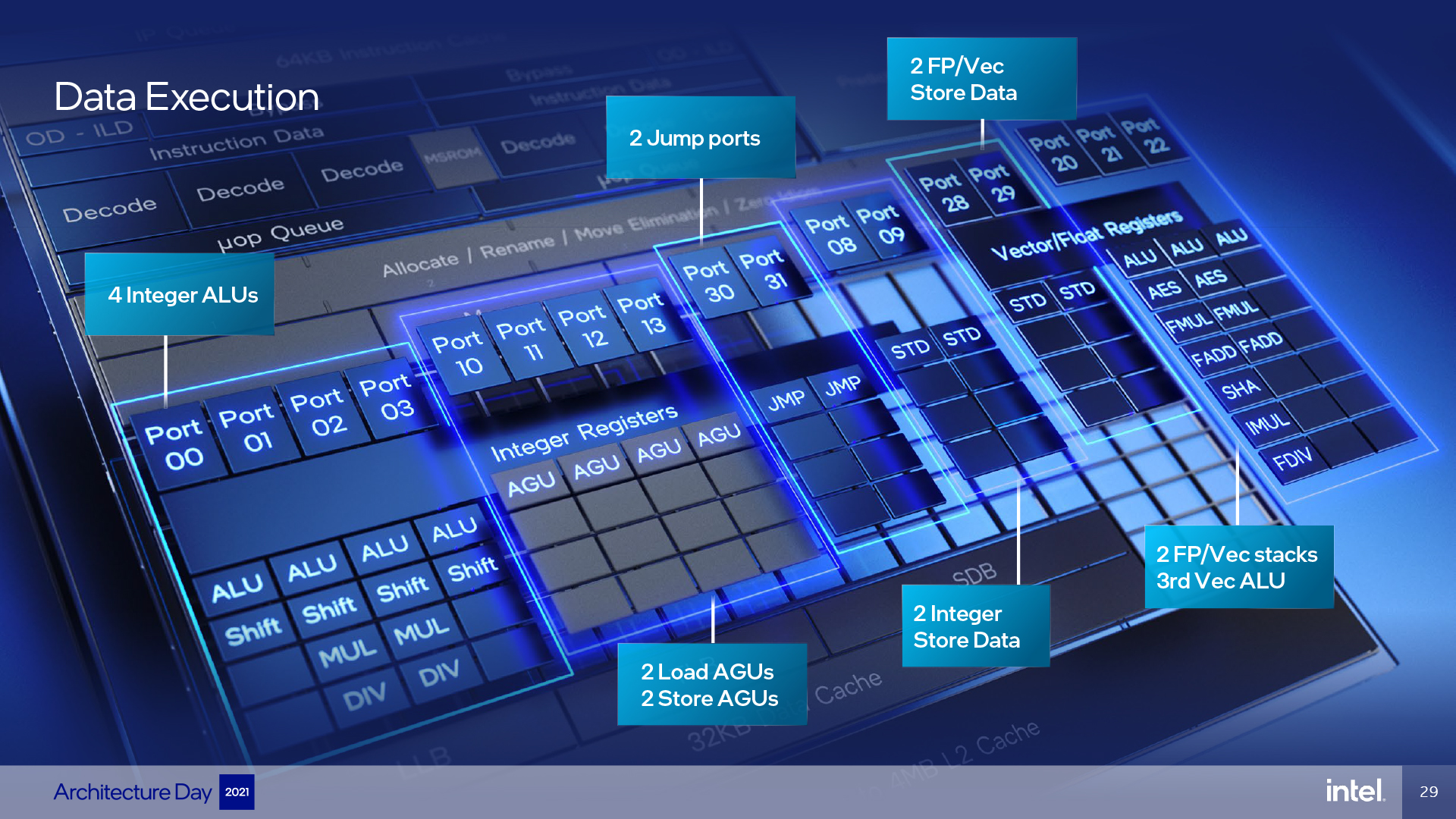

- 寬廣的後端每週期支援 5 條分派(five-wide allocation)和 8 條引退(eight-wide retire),256 條目亂序視窗和 17 個執行埠。

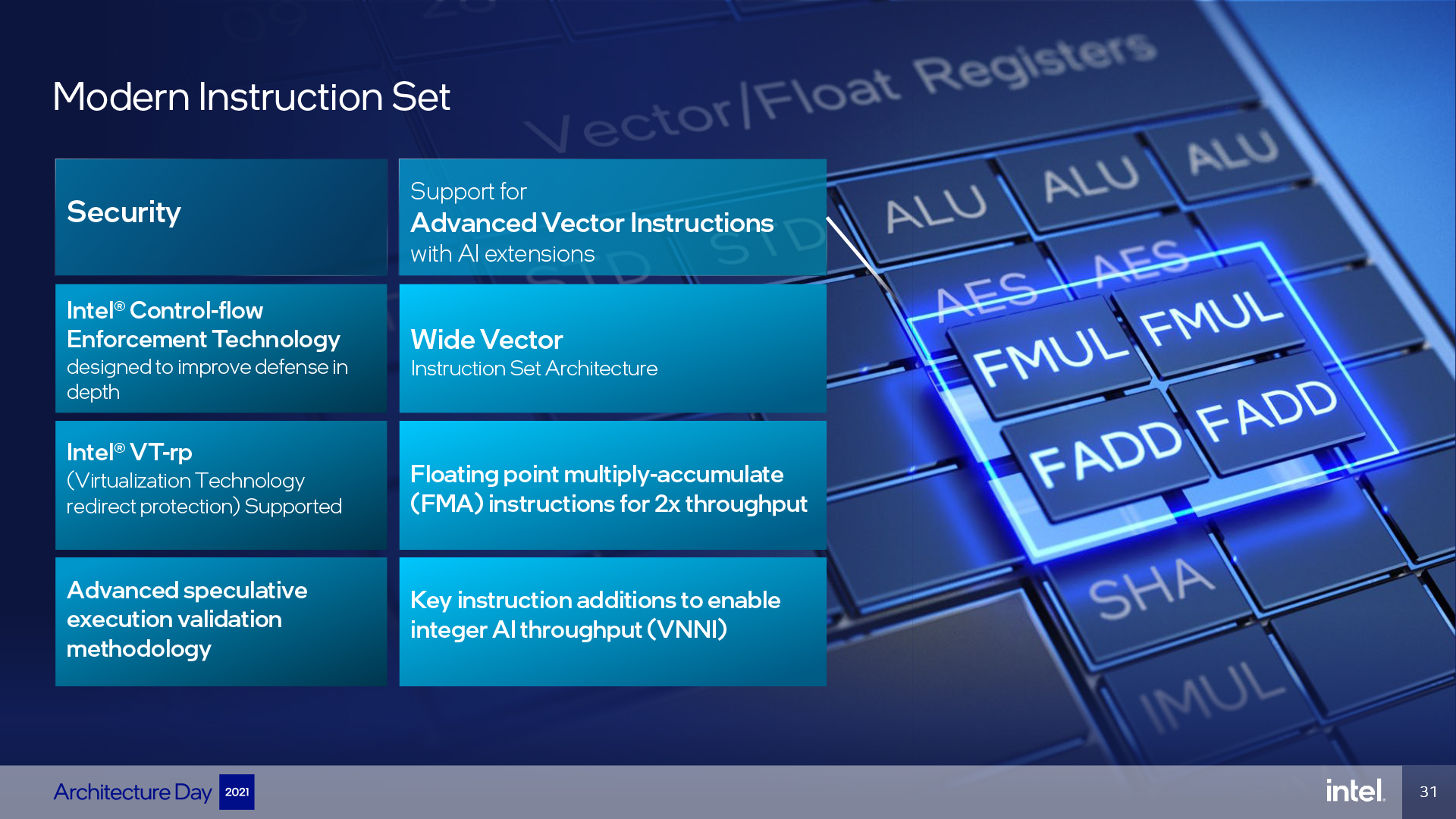

- 強式安全功能支援 Intel Control-Flow Enforcement Technology 以及 Intel Virtualization Technology Redirection Protection。

- 導入 AVX 指令集架構,並支援整數人工智慧(AI)運算的新延伸指令集。

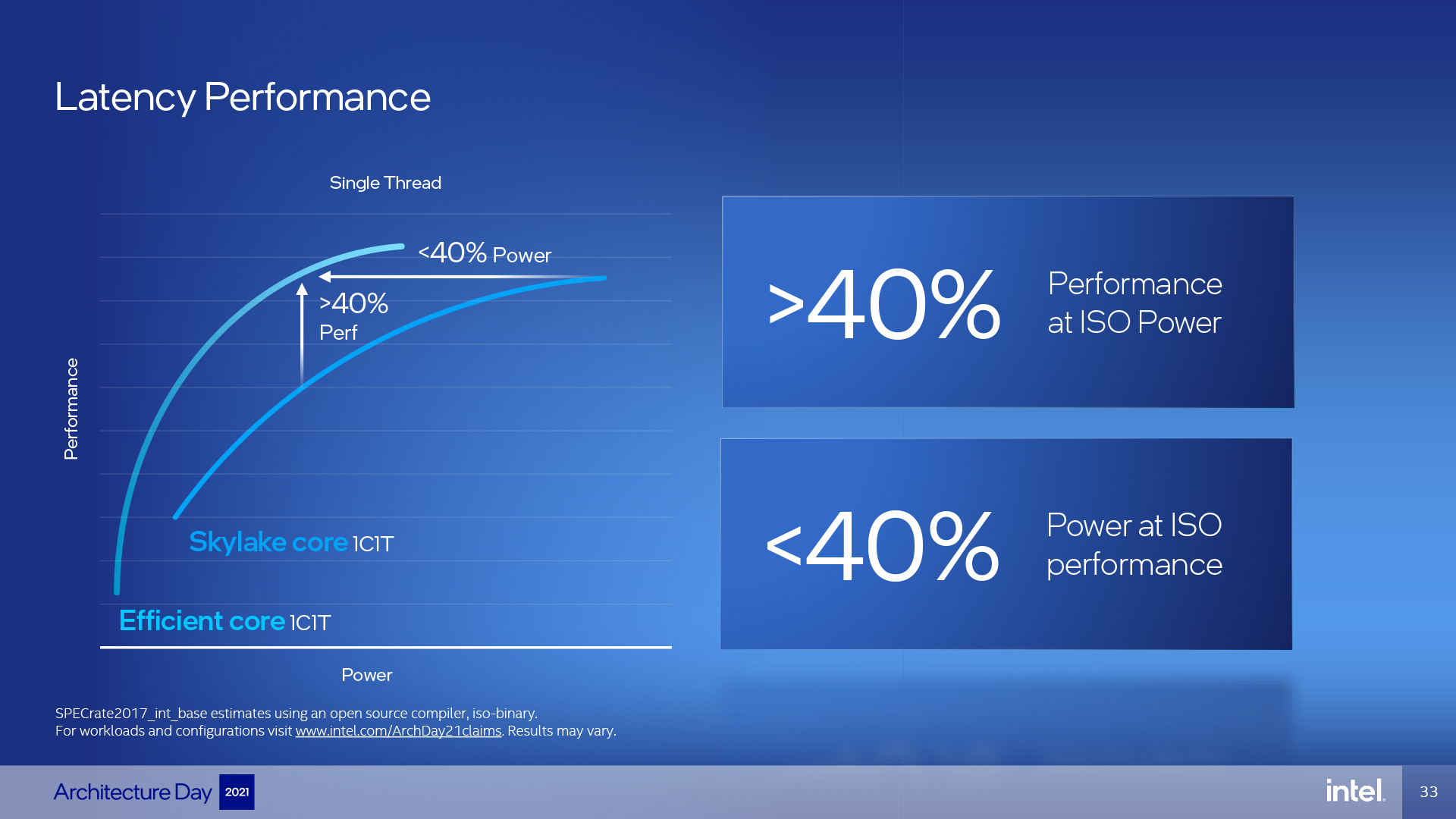

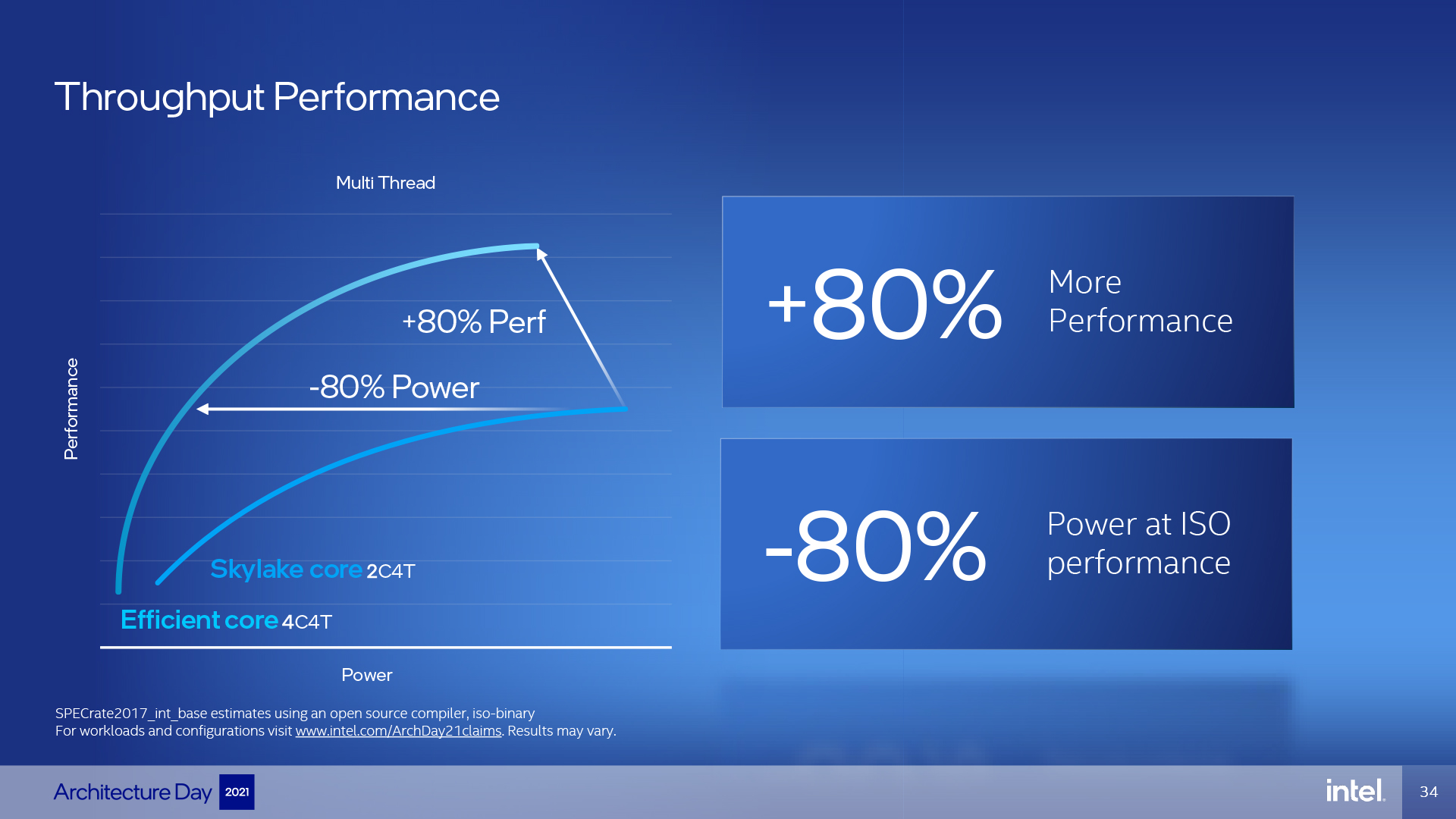

對照 Skylake CPU,單執行緒條件下效率核心可在相同功耗提升 40% 效能,或是在相同效能下降低 40% 功耗。若將執行緒提升為 4 條,對比 2 核心/4 執行緒的 Skylake CPU,4 顆效率核心可在相同提升 80% 效能,或是在相同效能下降低 80% 功耗。

Intel 表示,這是該公司歷來最具效率的 x86 微架構。

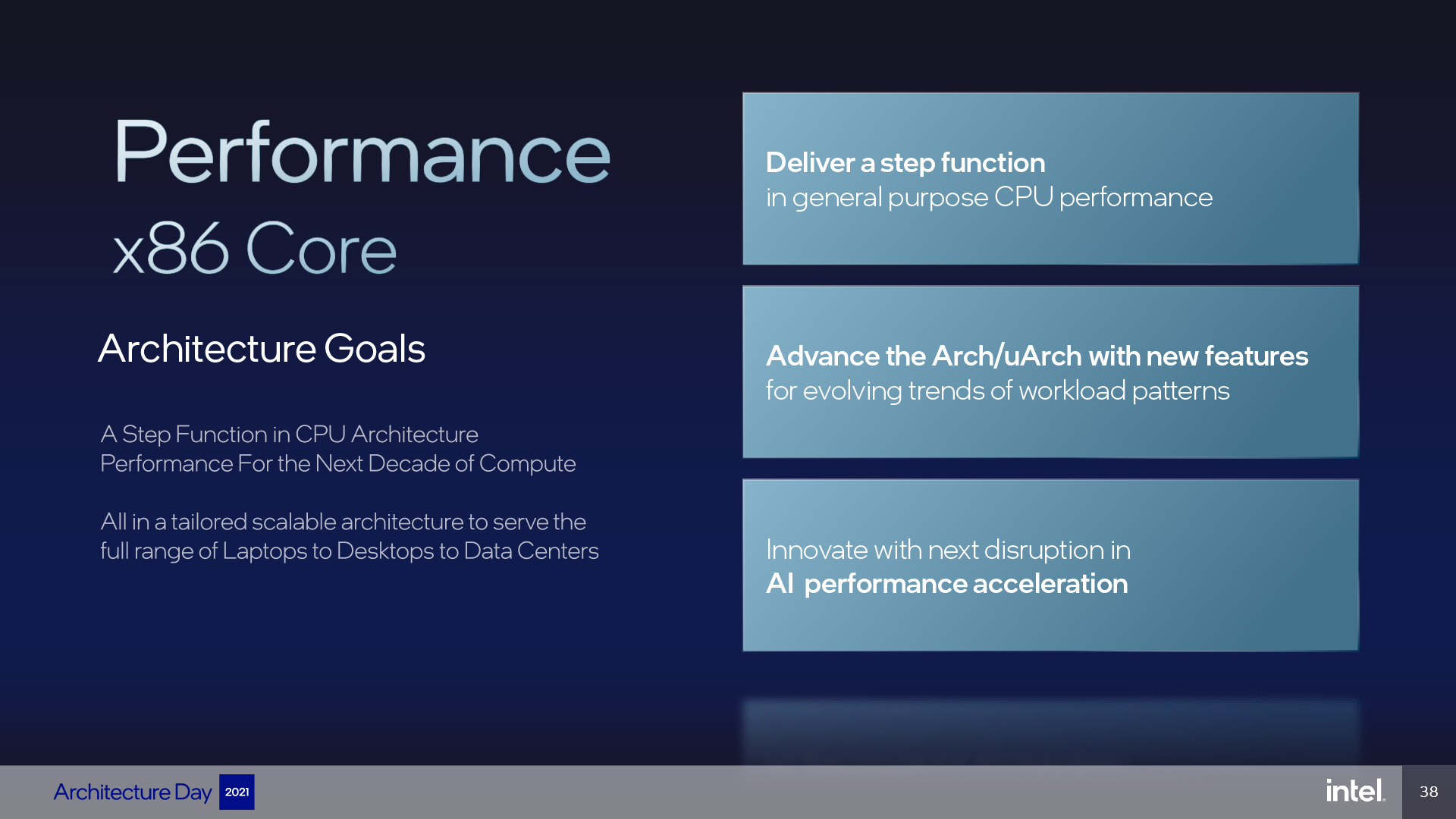

Performance Core (P-Core) 效能核心

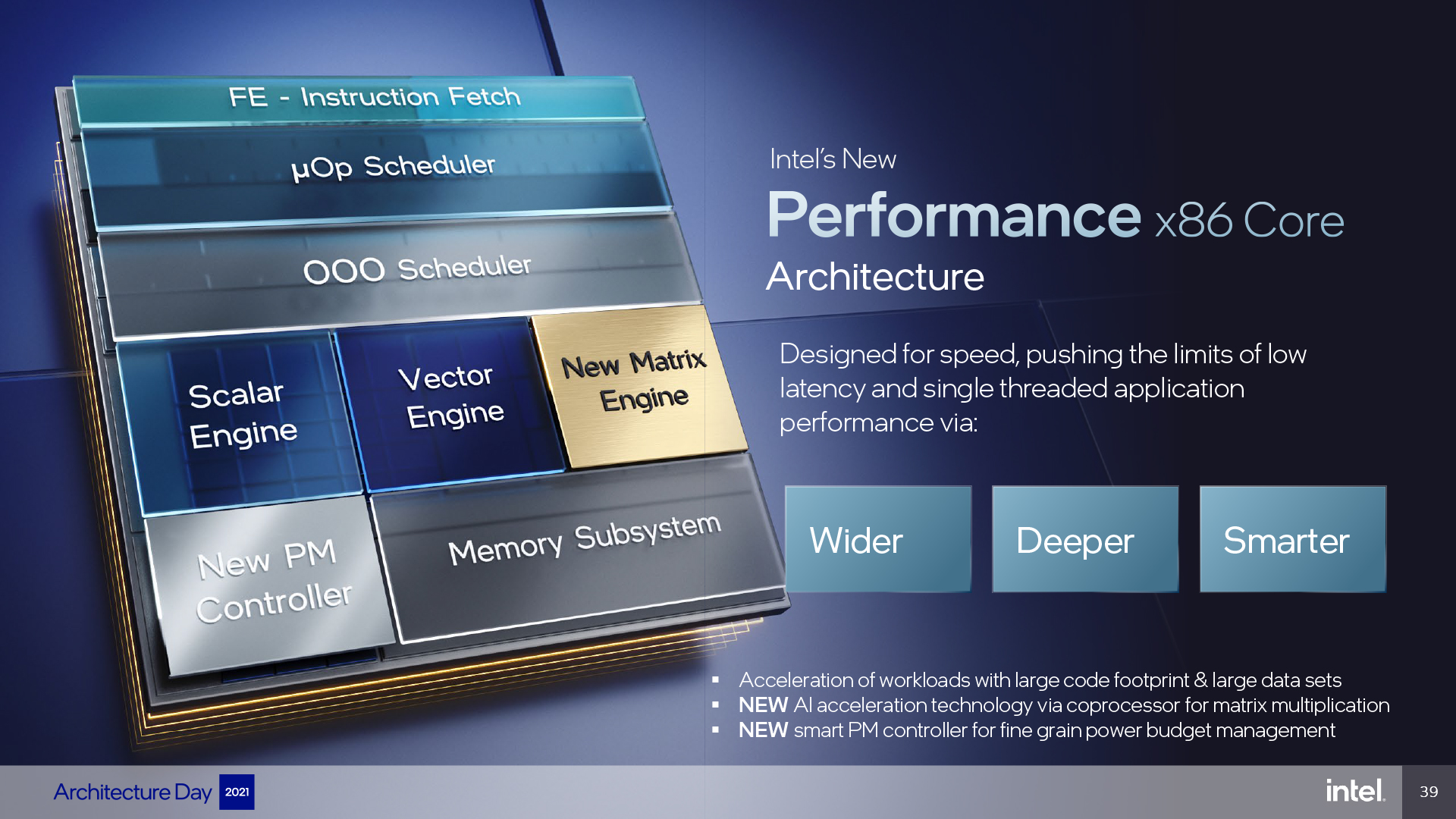

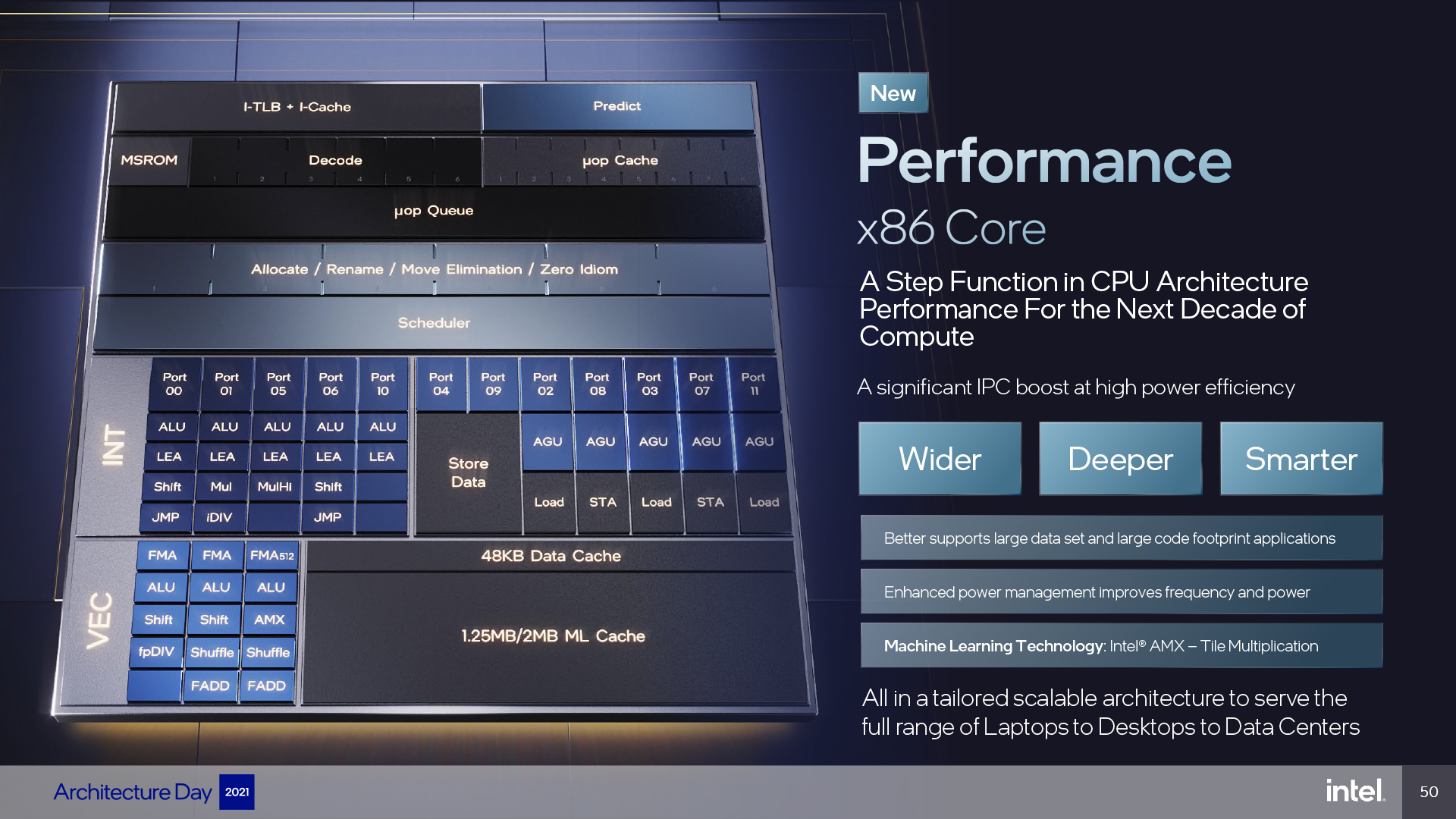

效能核心微架構先前的代號為 Golden Cove,專為複雜且龐大的單執行緒運算提供低延遲且強大的效能。不只提升大量資料與大型程式碼應用程式的支援性,強化的電源管理也成增進時脈與功耗表現。

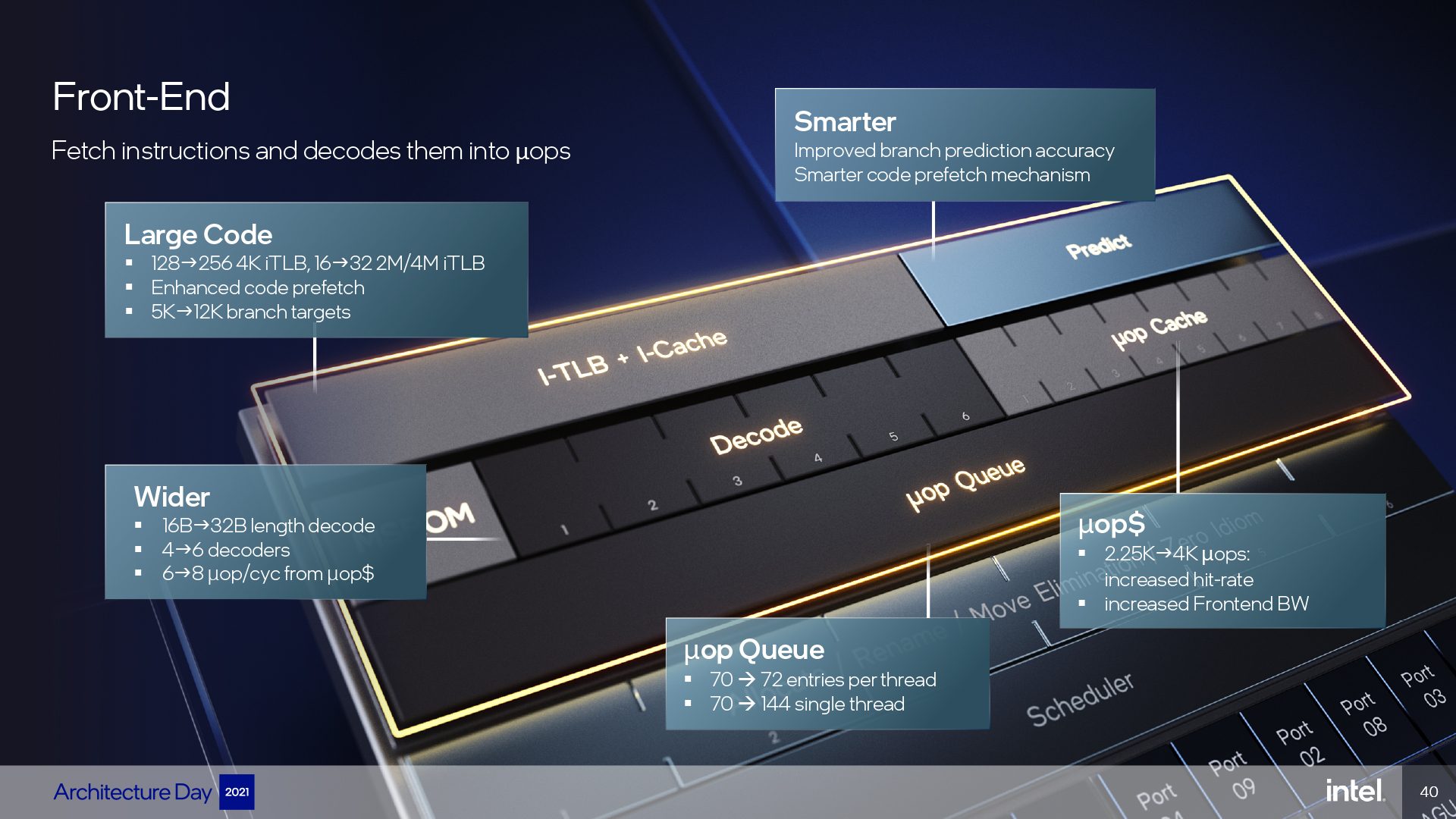

效能核心三大架構特性:

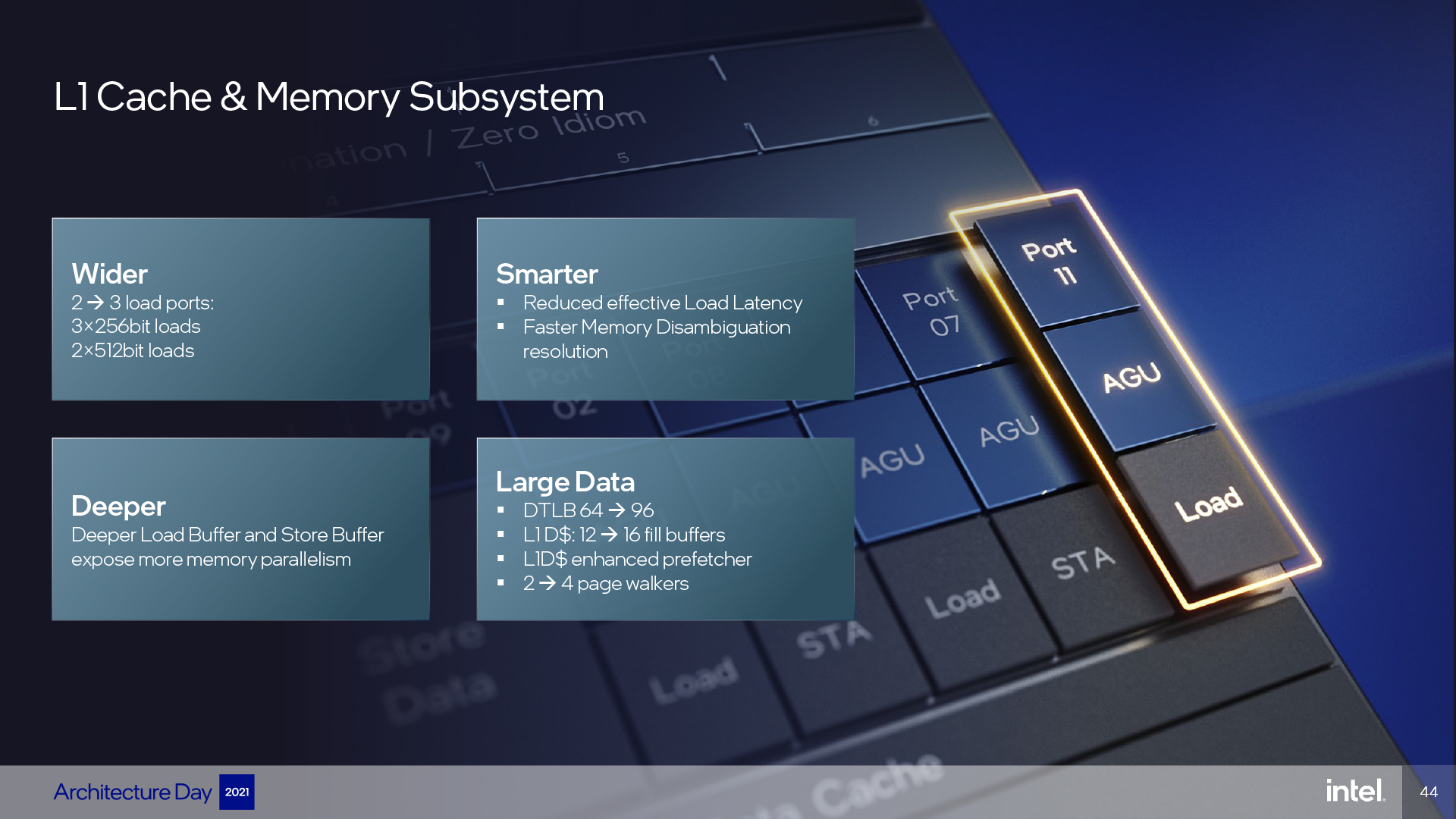

- 更寬:6 個解碼器(先前為4個);微指令(µop)快取每週期輸出 8 條(先前為6條);每週期6條分派(先前為5條);12 個執行埠(先前為10個)。

- 更深:更多的實體暫存器檔案;更深的 512 條目重排序緩衝區。

- 更聰明:改善分支預測精準度;降低有效 L1 延遲;L2 全快取寫入預測及頻寬最佳化。

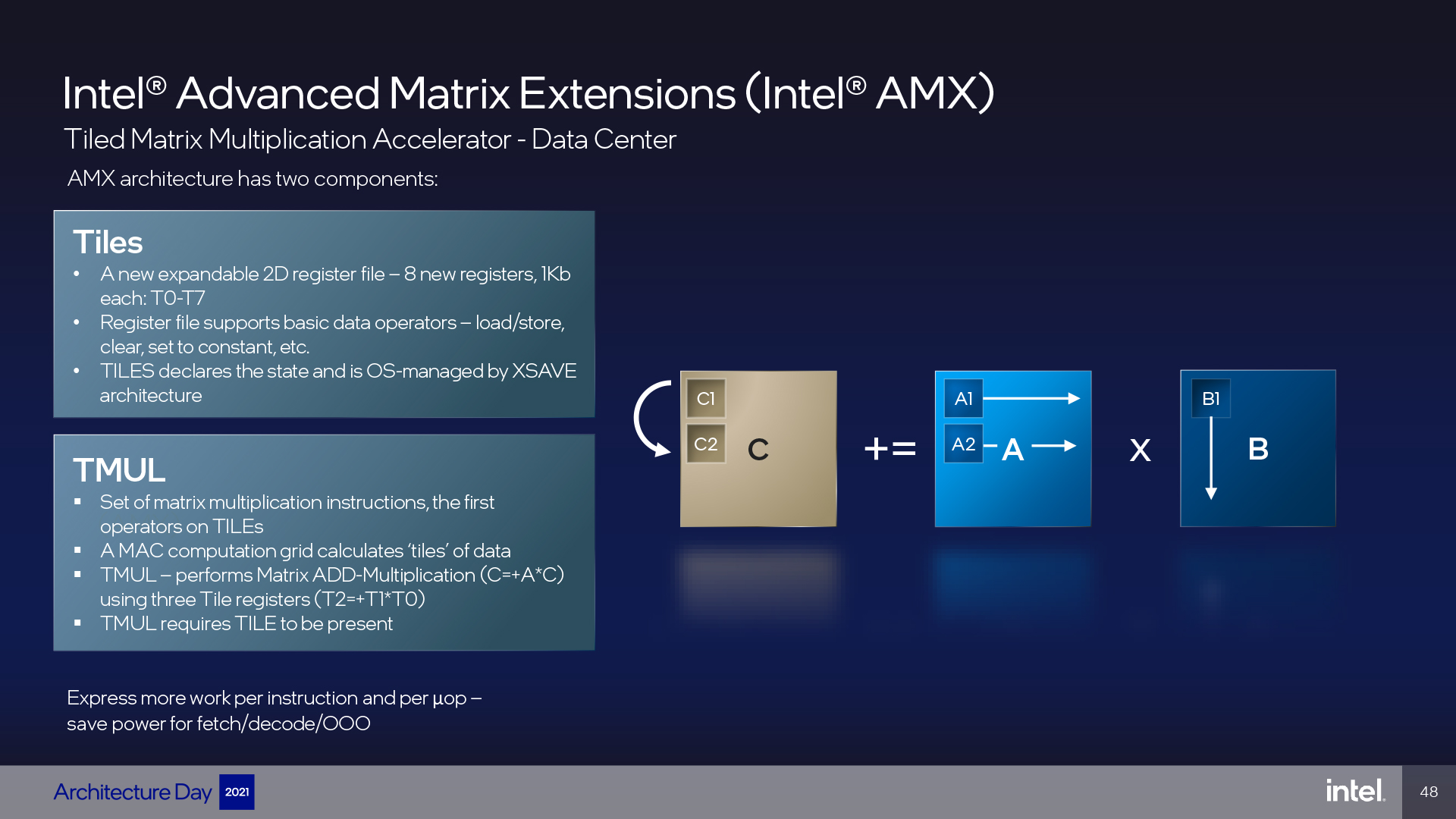

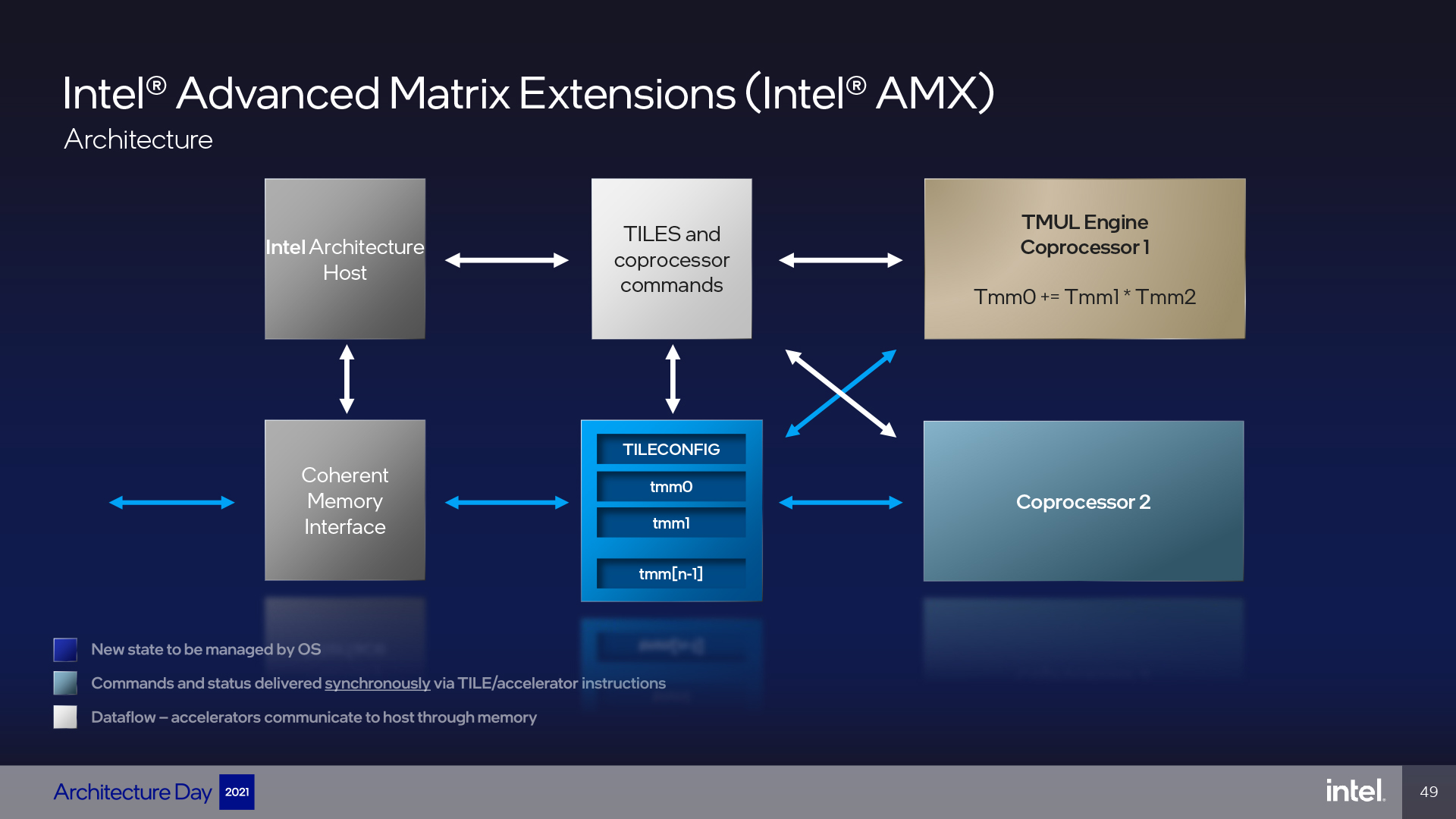

Intel 也導入 Advanced Matrix Extensions 技術,這是針對次代深度學習和訓練效能而發展的內建 AI 加速,內含專用硬體和新款指令集架構,能夠顯著地提升矩陣乘法運算速度。

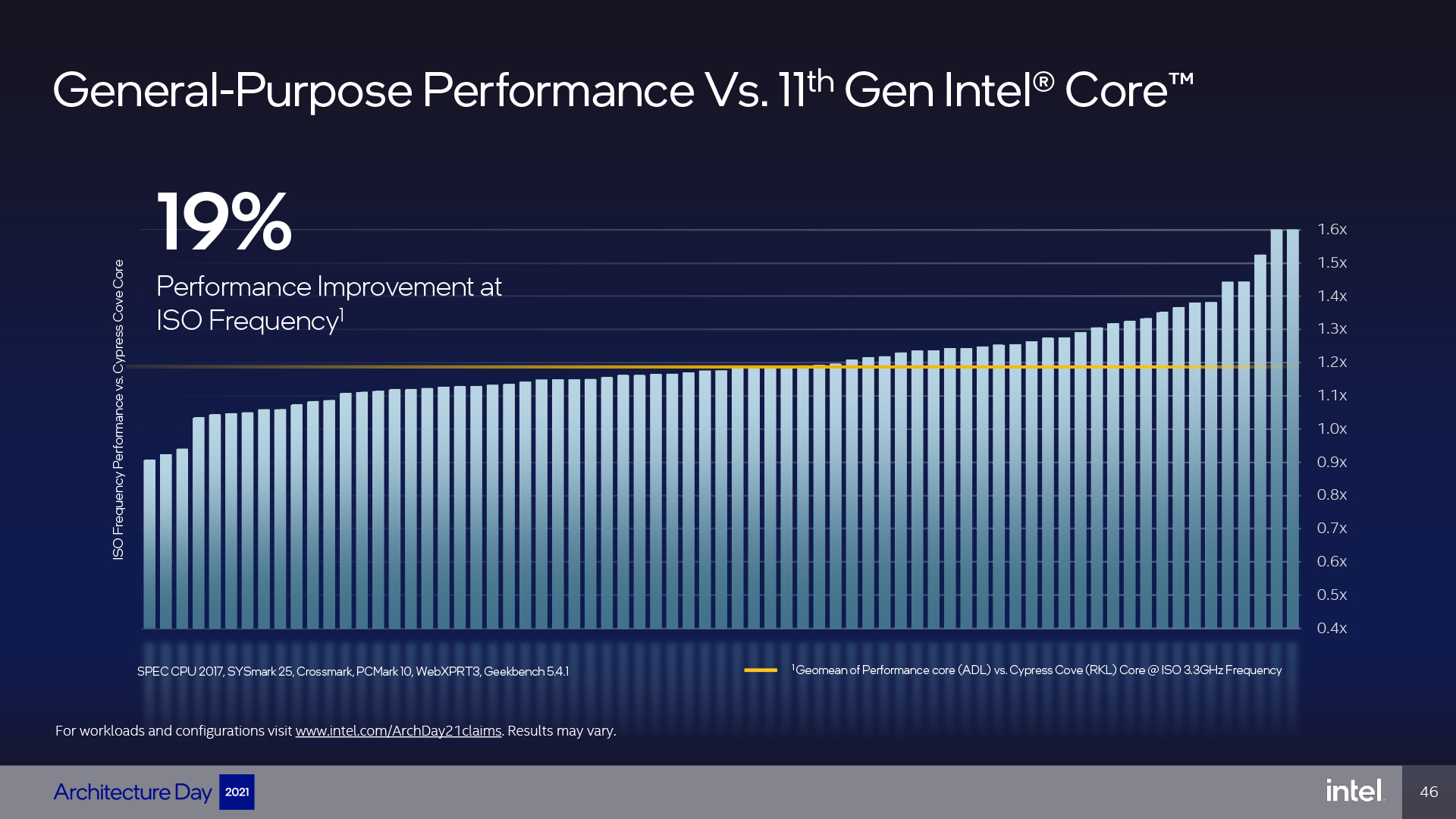

對照第 11 代 Core 處理器(Rocket Lake)的 Cypress Cove 微架構,效能核心在廣泛及多樣的工作負載能夠提供平均約 19% 的 IPC(每時脈週期指令數量)效能提升。更寬、更深的設計也能提升執行的平行度。

Intel 表示,這是該公司迄今最高效能的 CPU 核心,並將低延遲和單執行緒應用程式效能推向極限。

你對 Intel Alder Lake 的效能核心+效率核心架構有信心嗎?

- 有,大小核看起來有點厲害

- 沒有,我只要效能大核

- 不管啦,AMD Yes!

- 沒錢,哭啊